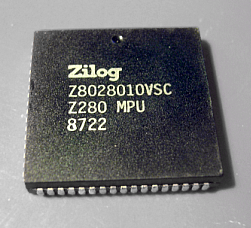

Zilog Z280

| Den här artikeln behöver källhänvisningar för att kunna verifieras. (2023-01) Åtgärda genom att lägga till pålitliga källor (gärna som fotnoter). Uppgifter utan källhänvisning kan ifrågasättas och tas bort utan att det behöver diskuteras på diskussionssidan. |

Zilog Z280 var en avancerad minidator-inspirerad version av processorn Z80 som lanserades i juli 1987. I grunden var det en något förbättrad CMOS-version av en tidigare Zilog Z800 från 1985, där dock båda blev kommersiella misslyckanden. De använde en så kallad MMU (Memory Management Unit) för att expandera adressrymden till 16 MB, och hade avancerade funktioner för multitasking, multiprocessor och slavprocessor-konfigurationer. Därutöver introducerades ett mycket stort antal nya instruktioner och adresseringsmoder (totalt över 2000 kombinationer). Adress- och databussarna var multiplexade och den interna klockfrekvensen var dessutom 2 eller 4 gånger den externa (det vill säga en 16 MHz CPU med en 4 eller 8 MHz buss). En 256 bytes cache användes för att kompensera för denna skillnad - en anpassning till de långa accesstider överkomliga minneskretsar hade vid början av 1980-talet. Mer framgångsrika utökningar av Z80-arkitekturen är till exempel Hitachi HD64180 och Zilog eZ80.

Se vidare detaljer på Zilog Z800.